## Digital System Construction - 1

**FYSIKUM**

Lecture 5: Designing for FPGA

Frequently-asked questions/ Good design practice

Timing

Types and records in VHDL

Lab 4 intro: digital stopwatch

#### Frequently asked questions

- Do functions/processes "remember" the values of variables?

- Yes!

- → For example, a "counter" variable remembers the last count.

- Different from software, where function variables can be re-initialized each time the function is called

- Signal/port names:

- Can a signal in an architecture can have the same name as a port of one of the components?

- Yes!

```

port map (select => select, ....);

```

Good practice to propagate common signals throughout the design:

```

→ reset, clock, ...

```

#### Frequently asked questions

- How do you use (read from) the value of an output port within the architecture?

- You can't read outputs directly.

- If you need to, create a signal for internal use, and then assign that signal to the output port:

```

int_buf <= (int_buf and enable);

output <= int buf;

</pre>

```

- Another method is to declare a port as bi-directional (inout instead of out)

- Not recommended unless a bi-directional port is really needed for your design

#### Signals versus variables

Example: counting with a <u>signal</u>:

```

architecture behav of clk div is

signal count: std logic vector (3 downto 0);

signal slowck : std logic := '0';

begin

cproc : process(clk)

begin

if rising edge(clk) then

if (count = "1111") then

count <= "0000";

slowck <= not slowck;</pre>

else

count <= count + 1;</pre>

end if;

end if;

end process;

end behav;

```

count is only updated once in the process

#### Signals versus variables

#### Counting with a <u>variable</u>:

```

architecture behav of clk div is

signal slowck : std logic := '0';

begin

cproc : process(clk)

variable count : integer := 0;

begin

if rising edge(clk) then

count := count + 1;

if (count > 15) then

count := 0;

slowck <= not slowck;</pre>

end if;

end if;

end process;

end behav;

```

Only one signal needed outside the process

count can be changed more than once with variable assignment (:=)

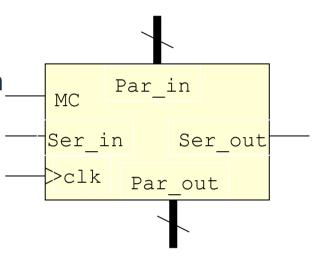

### Component port maps

Good to connect <u>named signals</u> to ports

Even if they are not used elsewhere, you can follow them while simulating

- Helps avoid accidental connections

- Inputs must <u>always</u> be connected

- Outputs don't need to be connected

- But unused logic is trimmed anyway

- Can also use: Par\_out => open

- Connect outputs to unique signals

- Avoid multiple drivers

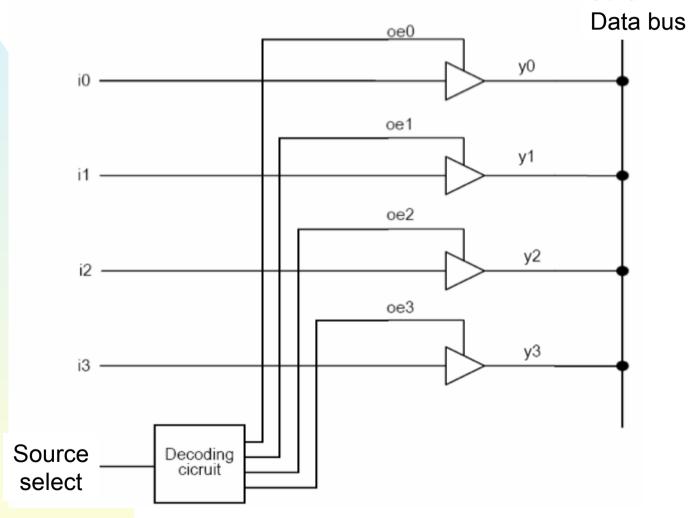

- ◆ Exception: Tri-state ('Z') connection to a bus

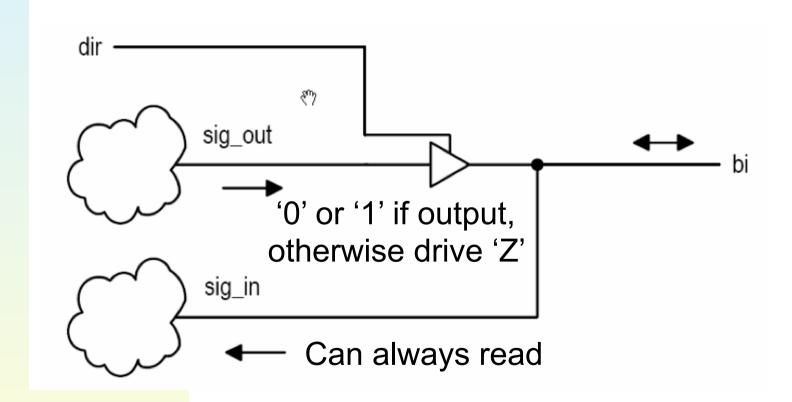

## Bi-directional signals (with tri-state)

### Implementing in VHDL

```

entity bus IO is

Port(Din: in std_logic;

Dout: out std logic;

IO pin: inout std logic;

wr en: in std logic );

end bus IO

buffer rw: process (Din, IOpin, wr en) -- can also be clocked

begin

if (wr en) then

IO pin <= 'Z'; -- high impedence if not driving

else

IO pin <= Dout;</pre>

end if;

end process;

```

#### Tri-state bus example

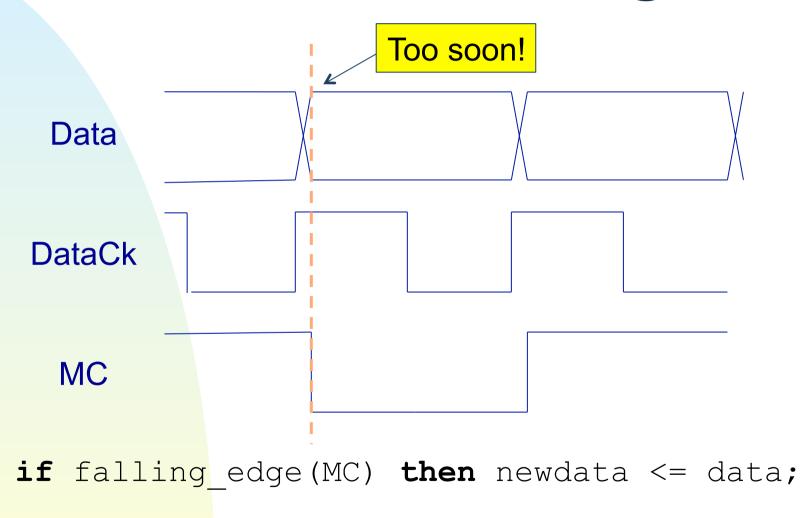

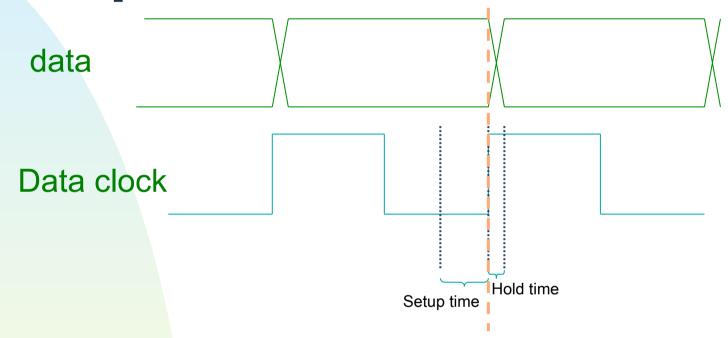

#### Be careful with timing...

## Flip-flops have minimum setup/hold times:

Setup time: Data must be stable before clock edge

Hold time: Time for flip-flop output to stabilize (short)

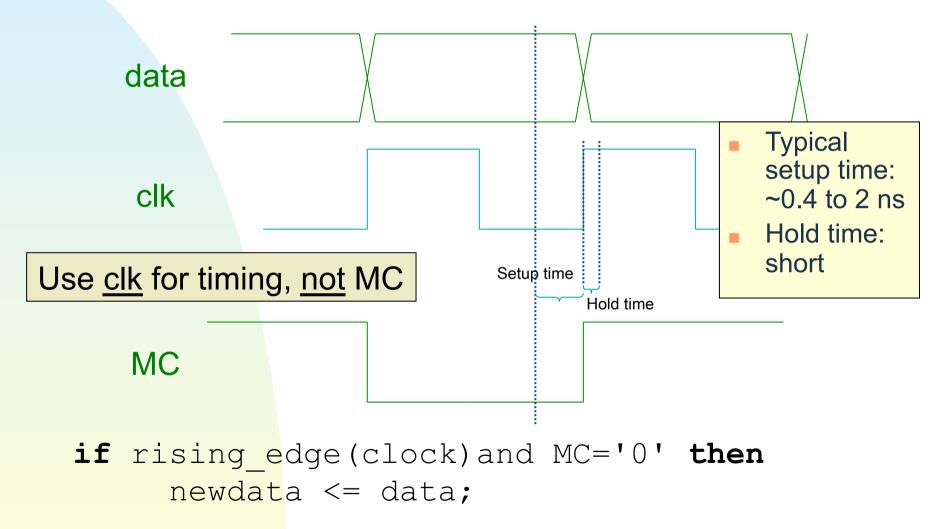

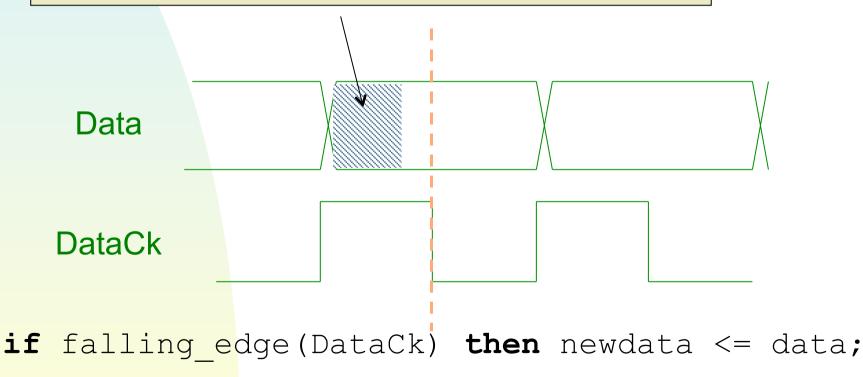

#### A better approach:

#### Even this can be risky:

New data can take some time to become valid (propagation delays, setup/hold times, etc)

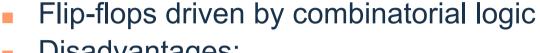

#### "Gated Clocks"

- Disadvantages:

- ◆ <u>Timing differences</u> between FFs driven by the same source (propagation)

- Unpredictable: hard to get good synthesis performance

- Gated clock edge degraded as more FFs load the same driver

- If you need to use a logic-derived signal to drive flip-flops, you can:

- Pass the logic output through a flip-flop (driven by another clock in your design), or

- Distribute the new timing signal through a global (or regional) FPGA clock buffer

#### Global clock buffers

- Distribute selected timing signals <u>synchronously</u>

- Inputs can be external timing signals, internally synthesized clocks, gated signals, etc

- Can use Clocking Wizard in IP Catalog

- 7-series global buffer in pure VHDL:

#### Good clocking practice

- Drive flip-flops with global clocks

- Use gated logic to "enable" clock

- Bring high-quality clocks to the FPGA

- Crystal oscillators have low jitter

- "Jitter cleaner" circuits can improve performance of non-crystal clocks

- Use designated clock pins, if available

- Designed for optimal input to global buffers

- Distribute internally-generated clocks via global or regional clock buffers as well

## Don't blindly trust the synthesis!

- Modern tools very powerful, but not perfect

- Some HDL descriptions can lead to non-optimal results

- Synthesis software doesn't know exactly what you want

- Optimal solution can't be <u>derived</u>, optimization process is an iterative search in a large "space" of possible solutions

- Good HDL code gives a good starting point for that search

- Pay attention to errors and warnings

- Even buggy designs can synthesize, but not work right!

- Check timing/mapping reports

- Constraints met? Reasonable resource use?

- Check RTL schematics in ISE

- Structure look like you expect?

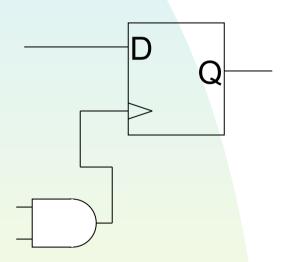

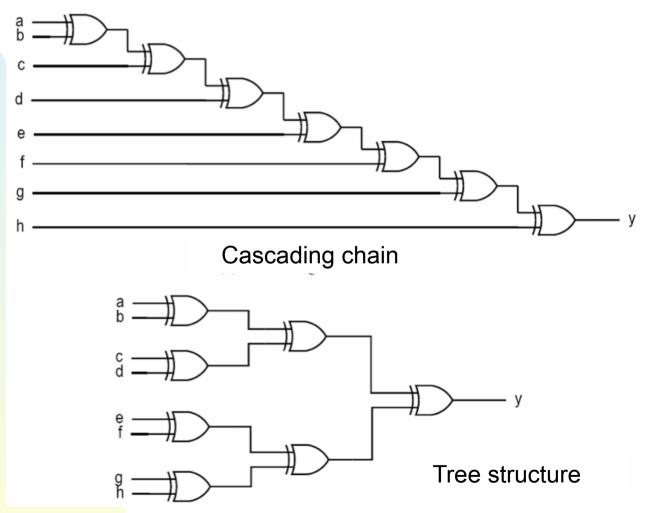

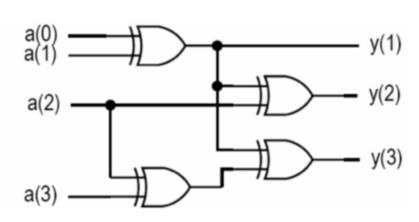

## Example: XOR cascading chain vs. tree structure

## Can choose to optimize for speed / area / both

Less logic (area)

Smaller delay (speed)

### **Types in VHDL**

#### **Constants and variables**

```

constant number_of_bytes : integer := 4;

constant number_of_bits : integer := 8*number_of_bytes;

constant e : real := 2.718281828;

constant prop_delay : time := 3 ns;

variable index: integer := 0;

variable start, finish : time := 0 ns;

```

- Constants can be declared globally (in architecture) or within sequential code (process, procedure, functions)

- Generally declared with a <u>value</u>

- Variables are declared in a piece of sequential code; not normally visible outside that process, etc.

### Scalar types

- A scalar type has <u>discrete</u> values

- No composite elements

- All values are <u>ordered</u>

- Each value has an implicit position number

- Predefined relational operators work

- Scalar types include:

- Numeric (integer, floating point)

- Physical (for example, time)

- Enumerated types

- integer is a scalar type representing all whole numbers representable on the <u>host computer</u>

#### Scalar types

Example of declaration and use in a package

### Floating-point types

Not usually used for synthesis

```

type input_level is range -10.0 to 10.0;

type probability is range 0.0 to 1.0;

variable input_A: input_level;

```

## Assignments use variables or constants of same type

```

type day_of_month is range 0 to 31;

type year is range 0 to 2100;

variable today: day_of_month := 19;

variable start_year: year := 2005;

```

Not legal to make this assignment:

```

start year := today;

```

## Integer/vector conversion in std\_logic\_unsigned

```

use ieee.std logic unsigned.all;

use ieee.std logic arith.conv std logic vector;

signal vector: std logic vector (v width downto 0);

integer int var;

--std logic to integer:

data types have

int var <= conv integer(vector);</pre>

attributes

--integer to std logic:

vector <= conv_std_logic vector(int var, vector'length);</pre>

```

#### Some useful VHDL attributes

- type'pos(value) -- integer position of value in the type

- type'val(i) -- value of type at integer position I

- array'length number of elements in an array/vector

- array'range -- range of an array/vector

- array'low -- lowest subscript of an array/vector

- Array'high -- highest subscript of an array/vector

- signal'event -- true if signal changes value

(Not an exhaustive list...)

### **Enumerated types**

#### Enumerated type attributes

- Each enumeration literal has an integer "position number" (0, 1, 2, 3, etc.)

- The first (left-most) enumeration literal has position 0, the next has position 1, etc.

- int\_variable <= alu\_function'pos(pass);</pre>

- ◆ alu\_option <= alu\_function'val(3);</pre>

subtract

#### Data types: Record

- Useful for bundling groups of signals

- Especially different signal types

- Example: CPU memory bus:

- + address(), data() -- vectors

- + read en, write en, chip sel -- bits

- + clock, reset timing

### Declaring and using records

```

type memory bus is record

address, data : std logic vector(15 downto 0);

rd_en, wr_en, c_sel : std_logic;

clk, reset : std logic;

end record;

signal address1 : std_logic_vector(15 downto 0);

signal bus1, bus2 : memory_bus;

bus1.address <= address1; -- Assign signal to record element

bus1.wr en <= '1'; -- Assign value to record element

bus2.data <= bus1.data; -- Copy part of a record</pre>

bus2 <= bus1; -- Copy entire record</pre>

```

#### Record example (ATLAS): L1Calo trigger topology processor (L1Topo)

#### Package: L1TopoDataTypes.vhd

```

library ieee;

use ieee.std logic 1164.all;

Package L1TopoDataTypes is

type ClusterTOB is record

Et: std logic vector (7 downto 0);

isol: std logic vector (4 downto 0);

eta: std logic vector (5 downto 0);

phi: std logic vector (5 downto 0);

end record:

Can declare with

type JetTOB is record

any width

Et1: std logic vector (8 downto 0);

Et2: std logic vector (9 downto 0);

eta: std logic vector (4 downto 0);

phi: std logic vector (4 downto 0);

end record;

type ClusterArray is array (natural range <>) of ClusterTOB;

type JetArray is array (natural range <>) of JetTOB;

-- After selection and sorting, use generic type for all TOBs.

type GenericTOB is record

Et : std logic vector (9 downto 0); -- Pad unused bits with zeros

eta: std logic vector (5 downto 0);

phi: std logic vector (5 downto 0);

end record;

type TOBArray is array (natural range <>) of GenericTOB;

33

end;

```

#### Using in an algorithm:

```

library ieee;

use ieee.std logic 1164.all;

use work.L1TopoDataTypes.all;

entity DeltaPhiIncl1 is

generic(InputWidth : integer := 8);

port (

: in TOBArray(InputWidth - 1 downto 0);

Tob

Parameters: in ParameterArray;

ClockBus : in std logic vector(2 downto 0);

Results : out std logic vector(NResultBits - 1 downto 0));

end DeltaPhiIncl1:

deltaPhi calc1: for i in 0 to (maxCount - 2) generate

deltaPhi calc2 : for j in (i + 1) to (maxCount - 1) generate

dphiCalc inst : entity work.DeltaPhiCalc

port map(

philIn => Tob(i).phi,

Compare all

phi2In => Tob(j).phi,

TOB pairs

deltaPhiOut => deltaPhi(i)(j)

);

end generate;

end generate;

```

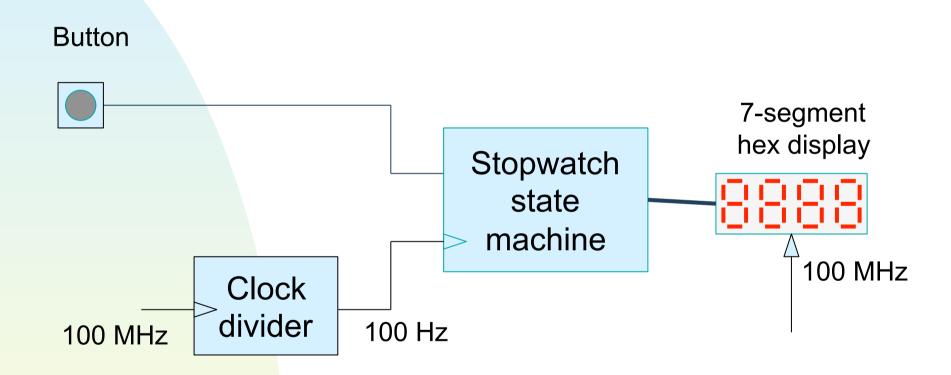

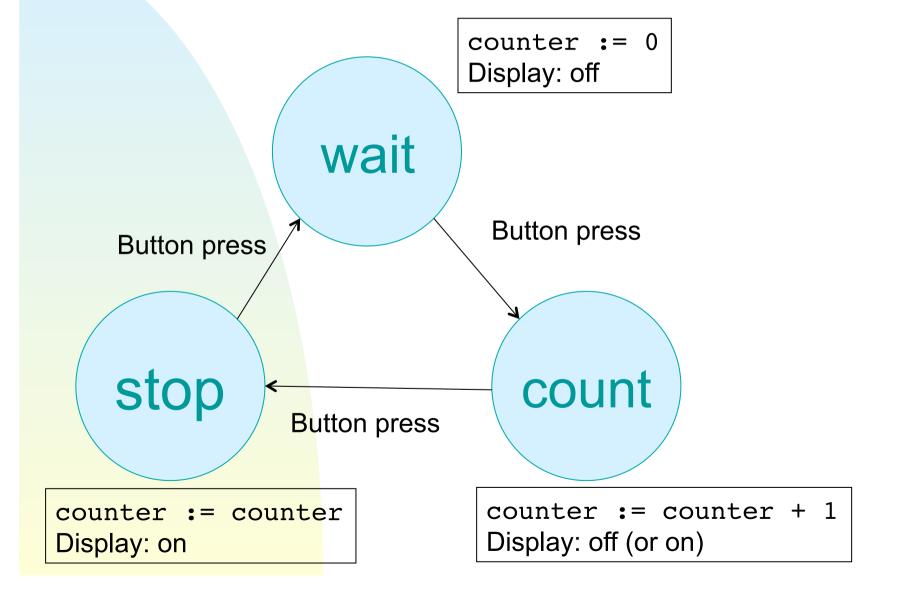

# Lab 4: Digital counter (stopwatch)

#### Basic stopwatch function

- Input: single pushbutton

- Output: 7-segment display

- ◆ (time to 1/100 second)

- Behavior:

- Push once: start timer

- Push again: stop, display time

- Push again: clear timer

### State diagram (simplified)

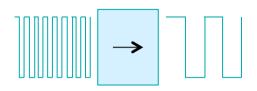

#### Clock divider

- Problem:

- ◆ FPGA has a <u>fast</u> clock (e.g. 100 MHz)

- ◆ We need a slow clock (100 Hz)

- Solution: a clock divider

- ◆ Internally a <u>counter</u>, clocked at 100 MHz

- Reset counter to zero every 0.01 s

- → Max count (100.000.000 / 100) = 1.000.000

- Good to have a <u>symmetric</u> output:

- ◆ If count < (1.000.000 / 2) then output <= '1'</p>

- Otherwise output <= '0';</p>

#### 'Debouncing' a button

Button Pressed

One approach: use a counter

(not needed for lab)

\ Logic "High"

Electrical signal from button:

Logic "Threshold"

Logic "Low"

Buttons on your lab boards are passively debounced (capacitor)

Logical signal seen at FPGA input:

Debounce circuit waits a few clock cycles before the output is allowed to fall:

### Stopwatch block diagram